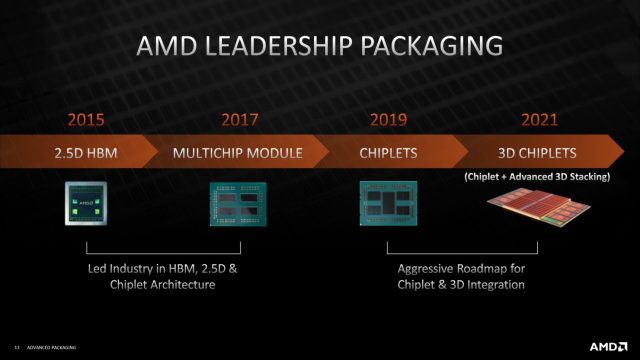

AMD, 3D V-Cache teknolojisi için yıllardır çalışıyor ve yakında bu teknolojiden yararlanan Zen 3 işlemciler bekliyoruz. Kırmızı ekip, gelecekte sunacağı Multi-Layer Chiplet Design (Çok Katmanlı Yonga Tasarımı) teknolojileriyle ilgili daha fazla ayrıntı verdi.

HotChips 33‘te yapılan sunumda yaklaşan ve gelecekte olan çeşitli eserler için 14 farklı mimari geliştirildiği söyleniyor. Ayrıyeten tasarım tekniğinin yonga mimarisinin performansına, gücüne, sunduğu alana ve ilgili eserin maliyetine bağlı olduğu belirtilmiş.

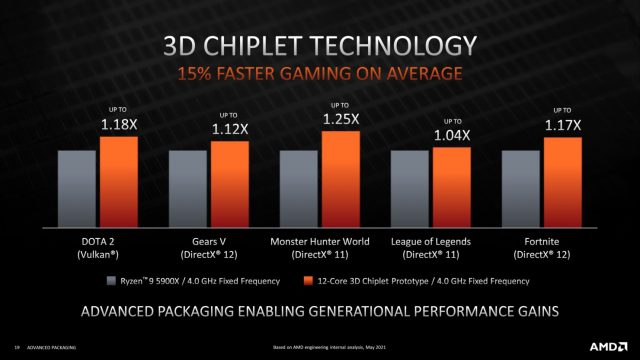

AMD’ye nazaran 3D Chiplet mimari dizaynının birinci tanıtımı 2021 yılı içerisinde gerçekleşecek. Tüketici ve sunucu tarafında 2D ve 2.5D tekniklerini aslında görmüştük, lakin 3D V-Cache ile birlikte sonunda 3D yonga teknolojisini göreceğiz. Birinci kullanıldığı eser ise ana Zen 3 CCD üzerinde bir SRAM önbelleğiyle gelecek bir Ryzen işlemci olacak. 3D chiplet teknolojisiyle düşük güç tüketiminin yanı sıra CPU içerisinde kullanılan alan azalıyor ve orta temasların yoğunluğu artıyor.

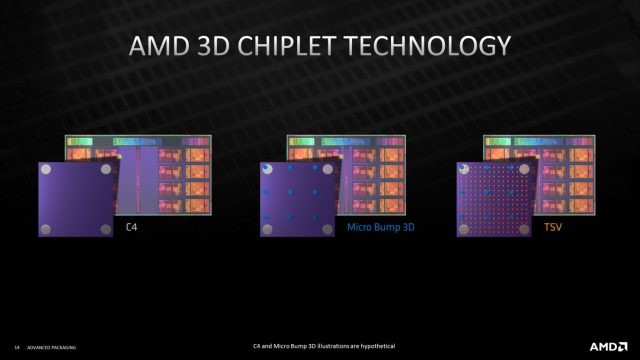

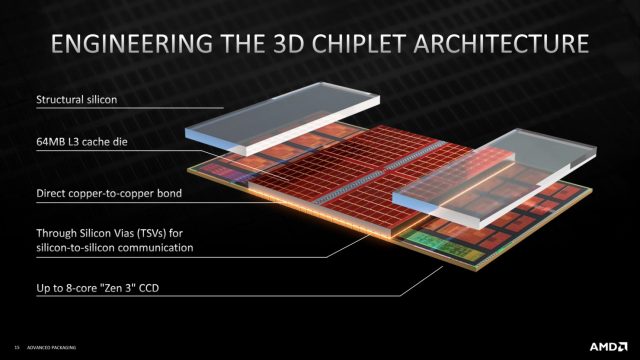

Kırmızı takım, 3D V-Cache teknolojisini Zen 3 CCD’sinin üzerine nasıl entegre ettiğini de paylaştı. Bunun için Micro Bump (3D) ve TSV (through-silicon vias-silikon üzerinden geçiş) orta temasları kullanıldı. Orta temas, TSMC ile derin bir paydaşlık içinde tasarlanmış ve optimize edilen, Direct CU-CU birleştirmesi ile yesyeni bir Dielectric-Dielectric Bonding tekniğini kullanıyor. Yani iki başka yonga bu teknoloji kullanılarak birbirine bağlanıyor.

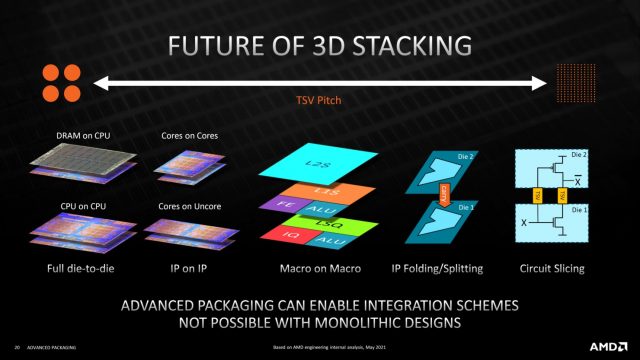

Teknoloji devi ayrıyeten CPU üzerindeki DRAM 3D istifleme teknolojisinde yalnızca yolun başlangıcında olduklarının altını çiziyor. Bu teknolojinin şu anda önbellek tarafında kullanıldığını hatırlatalım. Şirketin gelecekteki planı, çekirdekleri üst üste istiflemek ve küçük alanda çok daha fazla çekirdek sayısı elde etmek. Yüksek ihtimalle bunun gerçekleştiği günleri de göreceğiz ve bu sayede yüksek performans artışları yaşanacak.